# Z-Micro

## ZMCIS302x Low-Power Bidirectional I2C Isolators

#### 1 Key Features

- Bidirectional Data Transfer from DC to 2MHz

- Robust Galvanic Isolation of Digital Signals

- High lifetime: > 40 years

- Withstands up to 3.75kV<sub>RMS</sub> (narrow-body package), 5kV<sub>RMS</sub> (wide-body packages) and 7.5kV<sub>RMS</sub> (super wide-body packages) isolation rating for 60s (V<sub>ISO</sub>)

- ±150 kV/µs typical CMTI

- Schmitt trigger inputs for high noise immunity

- High electromagnetic immunity and withstands ±12.8kV surge voltage

- ±8kV Human Body Model ESD Protection

- 3.0V to 5.5V Wide Supply Operation

- Wide Operating Temperature Range: -40°C to 125°C

- RoHS-Compliant Packages

- Narrow-body SOIC8 (S) package

- Wide-body SOIC8-WB (G) package

- Wide-body SOIC16-WB (W) package

- Super Wide-body SOIC8-WWB (WG) package

- Open-drain Outputs

- 3.5mA Side A sink current capability

- 35mA Side B sink current capability

- Safety Regulatory Approvals

- VDE certification according to DIN EN IEC60747-17(VDE 0884-17):2021-10

- UL certification according to UL 1577

- CQC certification according to GB4943.1-2022

#### 2 Applications

- I<sup>2</sup>C, SMBus, PMBus<sup>™</sup> Interfaces

- Motor control systems

- Medical Equipment

- Battery Management

- Instrumentation

#### 3 Description

The ZMCIS302x devices are complete dual-channel, galvanic digital isolators with up to  $3.75 kV_{\text{RMS}}$  (narrow-

body package)/5kV<sub>RMS</sub> (wide-body package)/7.5kV<sub>RMS</sub> (super wide-body package) isolation rating and  $\pm 150$ kV/µs typical CMTI. All device versions have Schmitt trigger inputs for high noise immunity and each isolation channel has a logic input and output buffer separated by capacitive silicon dioxide (SiO<sub>2</sub>) insulation barrier to provide high electromagnetic immunity and low EMI. These devices feature high-integration design and only require fewer external components, V<sub>DDA</sub>, V<sub>DDB</sub> bypass capacitors and pull-up resistors, to build an isolated I<sup>2</sup>C interface.

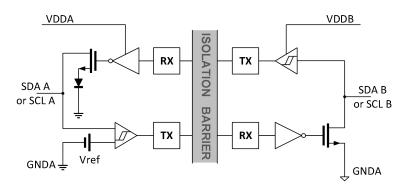

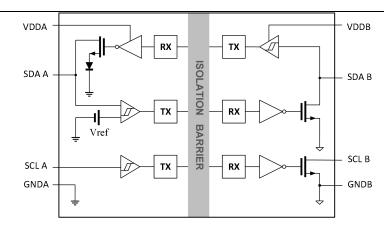

This family of devices operates from DC to 2MHz. The ZMCIS3020 offers two bidirectional, open-drain channels for applications, such as multi-master  $I^2C$ , that require data and clock to be transmitted in both directions on the same line. The ZMCIS3021 provides an isolated  $I^2C$  compatible interface supporting master mode only, with a unidirectional clock (SCL), and bidirectional data (SDA). All devices feature independent 3.0V to 5.5V supplies on each side of the isolator and the logic levels are set independently on either side by  $V_{DDA}$  and  $V_{DDB}$ . A simplified block diagram for a single ZMCIS302x bidirectional channel is shown in the figure below.

The ZMCIS302x series of devices are specified over -40°C to +125°C operating temperature range and are available in 8-pin SOIC narrow body package, 8-pin/16-pin SOIC wide body package and 8-pin SOIC super wide-body package. The wide temperature range and high isolation voltage make the devices ideal for use in harsh industrial environments.

#### **Device Information**

| PART NUMBER            | PACKAGE       | BODY SIZE (NOM)  |  |

|------------------------|---------------|------------------|--|

|                        | SOIC8(S)      | 4.90mm × 3.90mm  |  |

| ZMCIS3020<br>ZMCIS3021 | SOIC8-WB(G)   | 5.85mm × 7.50mm  |  |

|                        | SOIC16-WB(W)  | 10.30mm × 7.50mm |  |

| ZMCIS3020              | SOIC8-WWB(WG) | 6.40mm × 14.00mm |  |

#### ZMCIS302x Functional Block Diagram

#### 4 Ordering Guide

#### Table 4-1 Ordering Guide for Valid Ordering Part Number

| Part Number | # of Bidirectional<br>Channels | # of Unidirectional<br>Channels | Rated Voltage<br>(V <sub>RMS</sub> ) | Default Output | Package        |

|-------------|--------------------------------|---------------------------------|--------------------------------------|----------------|----------------|

| ZMCIS3020S  | 2                              | 0                               | 3.75                                 | Open drain     | SOIC8 (S)      |

| ZMCIS3020G  | 2                              | 0                               | 5.0                                  | Open drain     | SOIC8-WB (G)   |

| ZMCIS3020W  | 2                              | 0                               | 5.0                                  | Open drain     | SOIC16-WB (W)  |

| ZMCIS3020WG | 2                              | 0                               | 7.5                                  | Open drain     | SOIC8-WWB (WG) |

| ZMCIS3021S  | 1                              | 1                               | 3.75                                 | Open drain     | SOIC8 (S)      |

| ZMCIS3021G  | 1                              | 1                               | 5.0                                  | Open drain     | SOIC8-WB (G)   |

| ZMCIS3021W  | 1                              | 1                               | 5.0                                  | Open drain     | SOIC16-WB (W)  |

# **Table of Contents**

| 1 | Key Fe | eatures1                                | L |

|---|--------|-----------------------------------------|---|

| 2 | Applic | cations 1                               | L |

| 3 | Descr  | iption1                                 | L |

| 4 | Order  | ing Guide2                              | 2 |

| 5 | Revisi | on History 3                            | 5 |

| 6 | Pin De | escriptions and Functions4              | ŀ |

| 7 | Specif | ications6                               | ; |

|   | 7.1    | Absolute Maximum Ratings <sup>1</sup> 6 | 5 |

|   | 7.2    | ESD Ratings6                            | ; |

|   | 7.3    | Recommended Operating Conditions6       | ; |

|   | 7.4    | Thermal Information7                    |   |

|   | 7.5    | Power Ratings7                          | / |

|   | 7.6    | Insulation Specifications8              | 3 |

|   | 7.7    | Safety-Related Certifications           | ) |

|   | 7.8    | Electrical Characteristics 10           | ) |

|   | 7.9    | Supply Current Characteristics11        | - |

|   | 7.10   | Timing Requirements11                   | - |

|   |        |                                         |   |

|    | 7.11 | Timing Characteristics         | . 12 |

|----|------|--------------------------------|------|

| 8  | Para | ameter Measurement Information | 13   |

| 9  | Deta | ailed Description              | 14   |

|    | 9.1  | Overview                       | . 14 |

|    | 9.2  | Functional Block Diagrams      | .14  |

|    | 9.3  | Device Operation Modes         | . 15 |

| 10 |      | Application and Implementation | . 15 |

|    | 10.1 | Overview                       | . 15 |

|    | 10.2 | Typical Application            | . 16 |

| 11 |      | Package Information            | . 17 |

|    | 11.1 | SOIC8 (S) Package              | .17  |

|    | 11.2 | SOIC8-WB (G) Package           | . 18 |

|    | 11.3 | SOIC16-WB (W) Package          | . 19 |

|    | 11.4 | SOIC8-WWB (WG) Package         | . 20 |

| 12 |      | Soldering Information          | .21  |

| 13 |      | Soldering Information          | .22  |

| 14 |      | Important Notice错误!未定义书签       | 5.   |

## 5 Revision History

| <b>Revision Number</b> | Description                                                                                       | Revision Date | Page Changed                 |

|------------------------|---------------------------------------------------------------------------------------------------|---------------|------------------------------|

| Version 1.00           | N/A                                                                                               |               | N/A                          |

| Version 1.01           | Change POD and tape information                                                                   | 2023/02/09    | 18, 19, 20, 22               |

| Version 1.02           | Update VDE information                                                                            | 2023/09/13    | 8, 9                         |

| Version 1.03           | Update VDE, UL, CQC information<br>Update the test conditions of V <sub>IOSM</sub>                | 2024/04/13    | 1, 8, 9                      |

|                        | Add part number for SOIC8-WWB package: ZMCIS3020WG                                                |               | 1, 2, 4, 7, 8, 9, 14, 21, 23 |

| Version 1.04           | Update VDE information                                                                            | 2024/07/02    | 8, 9                         |

| version 1.04           | Update recommended land patterns for SOIC8, SOIC8-WB and SOIC16-WB                                | 2024/07/02    | 17, 18, 19                   |

|                        | Update recommended operation conditions for $V_{\text{ILA}}, V_{\text{ILB}}$ and $V_{\text{IHB}}$ | ]             | 6                            |

# **Z-Micro**

#### 6 Pin Descriptions and Functions

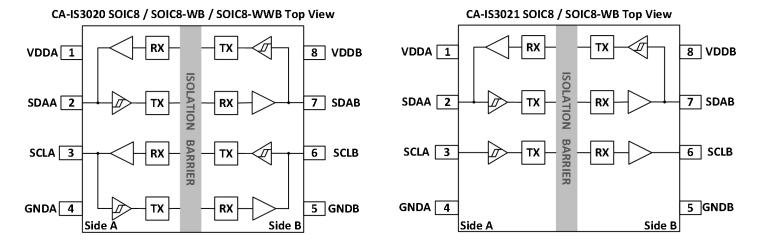

Figure 6-1 ZMCIS3020/ZMCIS3021 SOIC-8, SOIC8-WB and SOIC8-WWB Top View

| Pin Name | Pin Number | Туре                                                                                                                                                                                                                                                     | Description                                                                                              |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| VDDA     | 1          | Power                                                                                                                                                                                                                                                    | Power supply for side A.                                                                                 |

| SDAA     | 2          | 2     Digital I/O     Bidirectional data input/output on side A. SDAA is translated to/from and is an open-drain output.       3     Digital I/O     Bidirectional clock input/output on side A. SCLA is translated to/from and is an open-drain output. |                                                                                                          |

| SCLA     | 3          |                                                                                                                                                                                                                                                          |                                                                                                          |

| GNDA     | 4          | 4 Ground Ground reference for side A.                                                                                                                                                                                                                    |                                                                                                          |

| GNDB     | 5          | Ground                                                                                                                                                                                                                                                   | Ground reference for side B.                                                                             |

| SCLB     | 6          | Digital I/O                                                                                                                                                                                                                                              | Bidirectional clock input/output on side B. SCLB is translated to/from SCLA and is an open-drain output. |

| SDAB     | 7          | Digital I/O                                                                                                                                                                                                                                              | Bidirectional data input/output on side B. SDAB is translated to/from SDAA and is an open-drain output.  |

| VDDB     | 8          | Power                                                                                                                                                                                                                                                    | Power supply for side B.                                                                                 |

#### Table 6- 2 ZMCIS3021S/ZMCIS3021G Pin Description

| Pin name | Pin number                                                                                    | Туре          | Description                                                                |

|----------|-----------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------|

| VDDA     | 1 Power Power supply for side A.                                                              |               | Power supply for side A.                                                   |

| SDAA     | A 2 Digital I/O Bidirectional data input/output o                                             |               | Bidirectional data input/output on side A. SDAA is translated to/from SDAB |

| JDAA     | Ζ                                                                                             | Digital 1/0   | and is an open-drain output.                                               |

| SCLA     | 3                                                                                             | Digital Input | Clock input on side A. SCLA is translated to SCLB.                         |

| GNDA     | 4                                                                                             | Ground        | Ground reference for side A.                                               |

| GNDB     | 5                                                                                             | Ground        | Ground reference for side B.                                               |

|          | SCLB         6         Digital Output         Clock output on side B. SCLB is tranout output. |               | Clock output on side B. SCLB is translated from SCLA and is an open-drain  |

| JCLD     |                                                                                               |               | output.                                                                    |

| SDAB     | AB 7 Dig                                                                                      | Digital I/O   | Bidirectional data input/output on side B. SDAB is translated to/from SDAA |

| JUAD     |                                                                                               | Digital I/O   | and is an open-drain output.                                               |

| VDDB     | 8                                                                                             | Power         | Power supply for side B.                                                   |

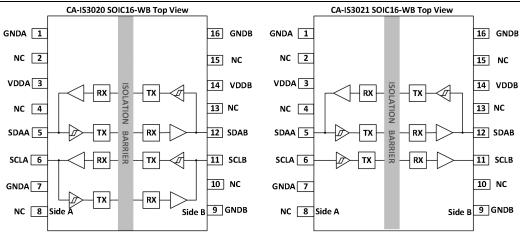

| Pin name | Pin number | Туре        | Description                                                                                              |

|----------|------------|-------------|----------------------------------------------------------------------------------------------------------|

| GNDA     | 1, 7       | Ground      | Ground reference for side A.                                                                             |

| NC       | 2, 4, 8    |             | No connect. Do not connect these pins externally.                                                        |

| VDDA     | 3          | Power       | Power supply for side A.                                                                                 |

| SDAA     | 5          | Digital I/O | Bidirectional data input/output on side A. SDAA is translated to/from SDAB and is an open-drain output.  |

| SCLA     | 6          | Digital I/O | Bidirectional clock input/output on side A. SCLA is translated to/from SCLB and is an open-drain output. |

| GNDB     | 9, 16      | Ground      | Ground reference for side B.                                                                             |

| NC       | 10, 13, 15 |             | No connect. Do not connect these pins externally.                                                        |

| SCLB     | 11         | Digital I/O | Bidirectional clock input/output on side B. SCLB is translated to/from SCLA and is an open-drain output. |

| SDAB     | 12         | Digital I/O | Bidirectional data input/output on side B. SDAB is translated to/from SDAA and is an open-drain output.  |

| VDDB     | 14         | Power       | Power supply for side B.                                                                                 |

#### Table 6-3 ZMCIS3020W Pin Description

#### Table 6-4 ZMCIS3021W Pin Description

| Pin name | Pin number                                                                                           | Туре                                                                                                             | Description                                                                                             |

|----------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| GNDA     | GNDA1, 7GroundGround reference for side A.NC2, 4, 8No connect. Do not connect these pins externally. |                                                                                                                  | Ground reference for side A.                                                                            |

| NC       |                                                                                                      |                                                                                                                  | No connect. Do not connect these pins externally.                                                       |

| VDDA     | 3                                                                                                    | Power                                                                                                            | Power supply for side A.                                                                                |

| SDAA     | 5                                                                                                    | 5 Digital I/O Bidirectional data input/output on side A. SDAA is translated to/from and is an open-drain output. |                                                                                                         |

| SCLA     | 6                                                                                                    | Digital Input                                                                                                    | Clock input on side A. SCLA is translated to SCLB.                                                      |

| GNDB     | 9, 16                                                                                                | Ground                                                                                                           | Ground reference for side B.                                                                            |

| NC       | 10, 13, 15                                                                                           |                                                                                                                  | No connect. Do not connect these pins externally.                                                       |

| SCLB     | 11                                                                                                   | Digital Output                                                                                                   | Clock output on side B. SCLB is translated from SCLA and is an open-drain output.                       |

| SDAB     | 12                                                                                                   | Digital I/O                                                                                                      | Bidirectional data input/output on side B. SDAB is translated to/from SDAA and is an open-drain output. |

| VDDB     | 14                                                                                                   | Power                                                                                                            | Power supply for side B.                                                                                |

#### 7 **Specifications**

#### 7.1 Absolute Maximum Ratings<sup>1</sup>

|                                     | PARAMETER                         | MIN  | MAX                 | UNIT |

|-------------------------------------|-----------------------------------|------|---------------------|------|

| V <sub>DDA</sub> , V <sub>DDB</sub> | Power supply voltage <sup>2</sup> | -0.5 | 6.0                 | V    |

| SDAA, SCLA                          | Input/Output voltage              | -0.5 | $V_{DDA} + 0.5^{3}$ | V    |

| SDAB, SCLB                          | Input/Output voltage              | -0.5 | $V_{DDB} + 0.5^{3}$ | V    |

| I <sub>OA</sub>                     | Output Current                    | -20  | 20                  | mA   |

| I <sub>OB</sub>                     | Output Current                    | -100 | 100                 | mA   |

| TJ                                  | Junction temperature              |      | 150                 | °C   |

| T <sub>STG</sub>                    | Storage temperature               | -65  | 150                 | °C   |

| Notos                               |                                   | ·    |                     |      |

Notes:

The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute 1. maximum rating conditions for extended periods may cause permanent damage to the device.

- All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GNDA or GNDB) and are peak voltage 2. values.

- 3. The maximum voltage must not exceed 6V.

#### 7.2 **ESD Ratings**

|                  |                                                                                                                    |                                                                                        | VALUE | UNIT |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|------|--|--|

| $V_{\text{ESD}}$ | Electrostatic discharge                                                                                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>1</sup>              | ±8000 | V    |  |  |

|                  |                                                                                                                    | Charged device model (CDM), per JEDEC Specification JESD22-C101, all pins <sup>2</sup> | ±2000 | V    |  |  |

| Not              | lotes:                                                                                                             |                                                                                        |       |      |  |  |

| 1.               | <ol> <li>Per JEDEC document JEP155, 500V HBM allows safe manufacturing of standard ESD control process.</li> </ol> |                                                                                        |       |      |  |  |

| ~                |                                                                                                                    |                                                                                        |       |      |  |  |

Per JEDEC document JEP157, 250V HBM allows safe manufacturing of standard ESD control process. 2.

#### 7.3 **Recommended Operating Conditions**

|                                        | PARAMETER                          | N   | 1IN                | MAX              | UNIT |

|----------------------------------------|------------------------------------|-----|--------------------|------------------|------|

| V <sub>DDA</sub> , V <sub>DDB</sub>    | Power supply voltage               | 3   | 8.0                | 5.5              | V    |

| V <sub>SDDA</sub> , V <sub>VSCLA</sub> | A side input voltage               |     | 0                  | V <sub>DDA</sub> | V    |

| V <sub>SDDB</sub> , V <sub>VSCLB</sub> | B side input voltage               |     | 0                  | V <sub>DDB</sub> | V    |

| V <sub>ILA</sub>                       | A side Input low voltage           |     | 0                  | 0.47             | V    |

| V <sub>IHA</sub>                       | A side Input high voltage          | 0.7 | K V <sub>DDA</sub> | V <sub>DDA</sub> | V    |

| V <sub>ILB</sub>                       | B side Input low voltage           |     | 0                  | 0.8              | V    |

| V <sub>IHB</sub>                       | B side Input high voltage          |     | 2                  | V <sub>DDB</sub> | V    |

| I <sub>OLA</sub>                       | A side Output current (low level)  | (   | ).5                | 3.5              | mA   |

| I <sub>OLB</sub>                       | B side Output current (low level)  | (   | ).5                | 35               | mA   |

| C <sub>A</sub>                         | Maximum load capacitance on A side |     |                    | 40               | pF   |

| C <sub>B</sub>                         | Maximum load capacitance on B side |     |                    | 400              | pF   |

| f <sub>MAX</sub> 1                     | Maximum Frequency                  |     |                    | 2                | MHz  |

| T <sub>A</sub>                         | Environmental temperature          | -   | 40                 | 125              | °C   |

| Tj                                     | Junction temperature               | -   | 40                 | 150              | °C   |

| Note:                                  |                                    | 1   |                    |                  |      |

1. This maximum signal transmission rate is the maximum signal frequency at the maximum bus capacitance load and the maximum pull-down current. If the capacitance load is smaller, a higher signal transmission rate is possible.

**Z-Micro**

7.4 Thermal Information

| THERMAL METRIC   |                                        | ZMCIS302x |              |               |                |      |

|------------------|----------------------------------------|-----------|--------------|---------------|----------------|------|

|                  |                                        | SOIC8 (S) | SOIC8-WB (G) | SOIC16-WB (W) | SOIC8-WWB (WG) | UNIT |

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance | 109.0     | 92.3         | 86.5          | 68.3           | °C/W |

#### 7.5 Power Ratings

|                 | PARAMETER                              | TEST CONDITIONS                                                   | MIN | ТҮР | MAX | Unit |

|-----------------|----------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| PD              | Maximum power dissipation (both sides) |                                                                   |     |     | 86  | mW   |

| P <sub>DA</sub> | Maximum power dissipation (side-A)     | $V_{DDA} = V_{DDB} = 5.5V, T_J = 150^{\circ}C, C_A = 40pF, C_B =$ |     |     | 34  | mW   |

| P <sub>DB</sub> | Maximum power dissipation (side-B)     | 400pF; Input a 1-MHz 50% duty cycle clock signal                  |     |     | 52  | mW   |

#### ZMCIS3020, ZMCIS3021

Version 1.04

#### 7.6 Insulation Specifications

|                                              | Parameters Test conditions                        |                                                                                                                                                                                                                                                                                                      |       | Valu  | ue    |       | Unit            |

|----------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-----------------|

|                                              | Parameters                                        | lest conditions                                                                                                                                                                                                                                                                                      | S     | G     | W     | WG    | Unit            |

| CLR                                          | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                                                                                                                                                                                                                                                   | 4     | 8     | 8     | 15    | mm              |

| CPG                                          | External creepage <sup>1</sup>                    | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                                                                                                    | 4     | 8     | 8     | 15    | mm              |

| DTI                                          | Distance through the<br>insulation                | Minimum internal gap (internal clearance)                                                                                                                                                                                                                                                            | 28    | 28    | 28    | 28    | μm              |

| СТІ                                          | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                                                                                                                                | >600  | >600  | >600  | >600  | v               |

|                                              | Material group                                    | In accordance with IEC 60664-1                                                                                                                                                                                                                                                                       | Ι     |       | I     | I     |                 |

|                                              |                                                   | Rated mains voltage ≤ 150V <sub>RMS</sub>                                                                                                                                                                                                                                                            | I-IV  | I-IV  | I-IV  | I-IV  |                 |

|                                              |                                                   | Rated mains voltage ≤ 300V <sub>RMS</sub>                                                                                                                                                                                                                                                            | I-IV  | I-IV  | I-IV  | I-IV  | 1               |

| EC 6066                                      | 64-1 over-voltage category                        | Rated mains voltage ≤ 600V <sub>RMS</sub>                                                                                                                                                                                                                                                            | N/A   | I-IV  | I-IV  | I-IV  | 1               |

|                                              |                                                   | Rated mains voltage ≤ 1000V <sub>RMS</sub>                                                                                                                                                                                                                                                           | N/A   | -     | 1-111 | I-IV  | 1               |

| DIN V V                                      | DE V 0884-17:2021-10 <sup>2</sup>                 |                                                                                                                                                                                                                                                                                                      |       |       |       |       |                 |

| VIORM                                        | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                                                                                                                                                 | 566   | 1414  | 1414  | 2828  | VPF             |

| Maximum operating                            |                                                   | AC voltage; time-dependent dielectric breakdown<br>(TDDB) test                                                                                                                                                                                                                                       | 400   | 1000  | 1000  | 2000  | V <sub>RN</sub> |

| 10 1111                                      | isolation voltage                                 | DC voltage                                                                                                                                                                                                                                                                                           | 566   | 1414  | 1414  | 2828  | VD              |

| VIOTM Maximum transient<br>isolation voltage |                                                   | $V_{\text{TEST}} = V_{\text{IOTM}},$<br>t=60s (certified);<br>$V_{\text{TEST}} = 1.2 \times V_{\text{IOTM}},$<br>t=1 s (100% product test)                                                                                                                                                           | 5300  | 7070  | 7070  | 10600 | VP              |

| Vimp                                         | Maximum impulse voltage                           | 1.2/50-µs waveform per IEC 62368-1                                                                                                                                                                                                                                                                   | 5000  | 9846  | 9846  | 9846  | VP              |

| V <sub>IOSM</sub>                            | Maximum surge isolation<br>voltage <sup>3</sup>   | VIOSM $\ge$ 1.3 x VIMP; Tested in oil (qualification test),<br>1.2/50-µs waveform per IEC 62368-1                                                                                                                                                                                                    | 6500  | 12800 | 12800 | 12800 | VPR             |

|                                              |                                                   | Method a, after input/output safety test of the<br>sub-category 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ;<br>$V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10s$                                                                                                                                     | ≤5    | ≤5    | ≤5    | ≤5    |                 |

| q <sub>pd</sub>                              | Apparent charge <sup>4</sup>                      | Method a, after environmental test of the sub-<br>category 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ;<br>$V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10s$                                                                                                                                            | ≤5    | ≤5    | ≤5    | ≤5    | pC              |

|                                              |                                                   | $      Method b1, routine test (100\% production test) \\       and preprocessing (sample test) \\       V_{ini} = 1.2 \times V_{IOTM}, t_{ini} = 1s; \\        V_{pd(m)} = 1.875 \times V_{IORM}, t_m = 1s (certified, G/W/WG) \\        V_{pd(m)} = 1.5 \times V_{IORM}, t_m = 1s (certified, S) $ | ≤5    | ≤5    | ≤5    | ≤5    |                 |

| C <sub>IO</sub>                              | Barrier capacitance, input to output <sup>4</sup> | $V_{IO} = 0.4 \times \sin(2\pi ft), f = 1MHz$                                                                                                                                                                                                                                                        | ~0.5  | ~0.5  | ~0.5  | ~0.5  | pF              |

|                                              |                                                   | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                       | >1012 | >1012 | >1012 | >1012 |                 |

| RIO                                          | Isolation resistance <sup>5</sup>                 | $V_{10} = 500 \text{ V}, 100^{\circ}\text{C} \le T_A \le 125^{\circ}\text{C}$                                                                                                                                                                                                                        | >1011 | >1011 | >1011 | >1011 | Ω               |

|                                              |                                                   | V <sub>IO</sub> = 500 V at T <sub>s</sub> = 150°C                                                                                                                                                                                                                                                    | >109  | >109  | >109  | >109  | 1               |

|                                              | Contaminant level                                 |                                                                                                                                                                                                                                                                                                      | 2     | 2     | 2     | 2     |                 |

| JL 1577                                      |                                                   | 1                                                                                                                                                                                                                                                                                                    |       |       | 1     | 1     |                 |

|                                              |                                                   | V <sub>TEST</sub> = V <sub>ISO</sub> , t = 60s (certified)                                                                                                                                                                                                                                           |       |       |       |       |                 |

Notes:

1. Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

2. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

3. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

4. Apparent charge is electrical discharge caused by a partial discharge (pd).

5. All pins on each side of the barrier tied together creating a two-terminal device.

## 7.7 Safety-Related Certifications

| VDE                                                 | UL                             | CQC                                      |

|-----------------------------------------------------|--------------------------------|------------------------------------------|

| Certified according to DIN EN IEC60747-17(VDE 0884- | Certified according to UL 1577 | Certified according to GB4943.1-2022     |

| 17):2021-10; EN IEC60747- 17:2020+AC:2021           | Component Recognition Program  |                                          |

| Basic Isolation (SOIC8):                            | SOIC8: 3750VRMS                | SOIC8-WB / SOIC16-WB:                    |

| VIORM: 566V <sub>PK</sub>                           | SOIC8-WB: 5000VRMS             | Reinforced insulation (Altitude ≤ 5000m) |

| VIOTM: 5300V <sub>PK</sub>                          | SOIC16-WB: 5000VRMS            |                                          |

| VIOSM: 6500V <sub>PK</sub>                          | SOIC8-WWB: 7500VRMs (Pending)  |                                          |

| Reinforced Isolation (SOIC8-WB / SOIC16-WB):        |                                |                                          |

| VIORM: 1414V <sub>PK</sub>                          |                                |                                          |

| VIOTM: 7070V <sub>PK</sub>                          |                                |                                          |

| VIOSM: 12800V <sub>PK</sub>                         |                                |                                          |

| Reinforced Isolation (SOIC8-WWB): Pending           |                                |                                          |

| VIORM: 2828V <sub>PK</sub>                          |                                |                                          |

| VIOTM: 10600V <sub>PK</sub>                         |                                |                                          |

| VIOSM: 12800V <sub>PK</sub>                         |                                |                                          |

| Reinforced insulation Certificate number: 40057278  | Certificate number:            | Certificate number:                      |

| Basic insulation Certificate number: 40052786       | E511334                        | SOIC8-WB: CQC24001434134                 |

|                                                     |                                | SOIC16-WB: CQC23001406424                |

#### Version 1.04

#### **Electrical Characteristics** 7.8

Over recommended operating conditions, unless otherwise specified

| PARAMETER         |                                                                                                                 | TEST CONDITIONS                                                          | MIN  | ТҮР  | MAX  | UNIT  |

|-------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| Side A            | · · · ·                                                                                                         |                                                                          |      |      |      |       |

| VILTA             | Logic low input threshold<br>(SDAA and SCLA)                                                                    |                                                                          | 470  | 500  | 520  | mV    |

| VIHTA             | Logic high input threshold<br>(SDAA and SCLA)                                                                   |                                                                          | 500  | 560  | 620  | mV    |

| V <sub>HYSA</sub> | Voltage input hysteresis                                                                                        | VIHTA -VILTA                                                             | 40   | 60   | 80   | mV    |

| V <sub>OLA</sub>  | Logic low output voltage (SDAA and SCLA) $^{ m 1}$                                                              | $0.5 \text{mA} \leq (I_{SDAA} \text{ and } I_{SCLA}) \leq 3.5 \text{mA}$ | 630  | 700  | 760  | mV    |

| $\Delta V_{OITA}$ | Logic-low output voltage<br>to logic-high input voltage threshold<br>difference (SDAA and SCLA) <sup>1, 2</sup> | $0.5\text{mA} \leq (I_{SDAA} \text{ and } I_{SCLA}) \leq 3.5\text{mA}$   | 100  |      |      | mV    |

| Side B            |                                                                                                                 |                                                                          | 1    |      |      | •     |

| VILTB             | Logic low input threshold<br>(SDAB and SCLB)                                                                    |                                                                          | 1.13 | 1.33 | 1.53 | v     |

| V <sub>IHTB</sub> | Logic low output voltage<br>(SDAB and SCLB)                                                                     |                                                                          | 1.55 | 1.75 | 1.97 | V     |

| V <sub>HYSB</sub> | Voltage input hysteresis                                                                                        | V <sub>IHTB</sub> -V <sub>ILTB</sub>                                     | 0.30 | 0.42 | 0.54 | V     |

| V <sub>OLB</sub>  | Logic-low output voltage<br>(SDAB and SCLB)                                                                     | $0.5mA \le (I_{SDAB} \text{ and } I_{SCLB}) \le 35mA$                    |      |      | 0.4  | V     |

| Both Sides        |                                                                                                                 |                                                                          | 1    |      |      |       |

| .                 | Input leakage currents,<br>SDAA, SCLA, SDAA, and SCLA                                                           | $V_{SDAA} = V_{SCLA} = VDDA$<br>$V_{SDAB} = V_{SCLB} = VDDB$             |      |      | 1    | μΑ    |

| Cı                | Input capacitance to local ground<br>(SDA1, SCL1, SDA2, and SCL2)                                               |                                                                          |      | 3    |      | pF    |

| CMTI              | Common mode transient immunity                                                                                  | See Figure 8-3                                                           | ±100 | ±150 |      | kV/μs |

| V <sub>DDUV</sub> | VDD_ Undervoltage-lockout threshold <sup>3</sup>                                                                |                                                                          | 1.95 | 2.24 | 2.53 | V     |

| Notes:            |                                                                                                                 | 1                                                                        | 1    |      |      | 1     |

Not

This parameter applies to the ZMCIS3020 (SDAA, SCLA) and ZMCIS3021 SDAA bidirectional lines only. 1.

$\Delta V_{\text{OITA}} = V_{\text{OLA}} - V_{\text{IHTA}}$ . This is the minimum difference between logic-low output voltage and a logic-high input voltage. 2.

Any V<sub>DD</sub> voltage on both sides, less than the minimum will ensure device lockout. V<sub>DD</sub> voltage on both side A and side B greater than the 3. maximum will prevent device lockout.

**Z-Micro**

#### 7.9 Supply Current Characteristics

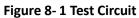

Over recommended operating conditions, unless otherwise specified, see Figure 8-1 for more information.

| PARAMETER                            | TEST CONDITIONS                                                     |                  | MIN TYP | MAX | UNIT |

|--------------------------------------|---------------------------------------------------------------------|------------------|---------|-----|------|

| $3V \le V_{DDA}, V_{DDB} \le 3.6V$   |                                                                     |                  |         |     |      |

|                                      | $V_{SDAA} = V_{SCLA} = GNDA; V_{SDAB} = V_{SCLB} = GNDB;$           | I <sub>DDA</sub> | 4.9     | 5.7 |      |

| ZMCIS3020                            | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | I <sub>DDB</sub> | 4.7     | 5.2 | -    |

| 21010135020                          | $V_{SDAA} = V_{SCLA} = V_{DDA}; V_{SDAB} = V_{SCLB} = V_{DDB};$     | I <sub>DDA</sub> | 2.4     | 2.8 |      |

|                                      | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 2.2     | 2.6 | mA   |

|                                      | $V_{SDAA} = V_{SCLA} = GNDA; V_{SDAB} = V_{SCLB} = GNDB;$           | DDA              | 2.9     | 4.4 |      |

| ZMCIS3021                            | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 2.4     | 3.7 |      |

| 21010135021                          | $V_{SDAA} = V_{SCLA} = V_{DDA}; V_{SDAB} = V_{SCLB} = V_{DDB};$     | DDA              | 1.7     | 2.6 |      |

|                                      | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 1.8     | 2.8 |      |

| $4.5V \le V_{DDA}, V_{DDB} \le 5.5V$ |                                                                     |                  |         |     |      |

|                                      | $V_{SDAA} = V_{SCLA} = GNDA; V_{SDAB} = V_{SCLB} = GNDB;$           | DDA              | 5.0     | 5.7 |      |

| ZMCIS3020                            | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 4.7     | 5.2 |      |

| 21010133020                          | $V_{SDAA} = V_{SCLA} = V_{DDA}$ ; $V_{SDAB} = V_{SCLB} = V_{DDB}$ ; | DDA              | 2.4     | 2.8 |      |

|                                      | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 2.2     | 2.6 | mA   |

| 7040(52021                           | $V_{SDAA} = V_{SCLA} = GNDA; V_{SDAB} = V_{SCLB} = GNDB;$           | DDA              | 3.0     | 4.5 |      |

|                                      | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 2.5     | 3.8 |      |

| ZMCIS3021                            | $V_{SDAA} = V_{SCLA} = V_{DDA}; V_{SDAB} = V_{SCLB} = V_{DDB};$     | DDA              | 1.8     | 2.7 |      |

|                                      | R1 = R2 = OPEN; C1 = C2 = OPEN                                      | DDB              | 1.9     | 2.9 |      |

#### 7.10 Timing Requirements

| PARAMETER                          | MIN | ТҮР | MAX | UNIT |

|------------------------------------|-----|-----|-----|------|

| t <sub>sP</sub> Input noise filter | 10  | 25  |     | ns   |

#### ZMCIS3020, ZMCIS3021

Version 1.04

#### 7.11 Timing Characteristics

**Z-Micro**

|                        |                                            |                                                                      | EST CONDITIONS                                                              | MIN | ТҮР | MAX | UNI |

|------------------------|--------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-----|

| 3V≤(V <sub>DDA</sub>   | , V <sub>DDB</sub> ) ≤ 3.6V                |                                                                      |                                                                             |     |     |     |     |

| t <sub>fA</sub>        | Fall Time (SDAA, SCLA)                     | See Figure 8-1<br>R1 = 953Ω                                          | A side input from 0.7 x $V_{DDA}$ to<br>0.3 x $V_{DDA}$                     | 18  | 23  | 28  |     |

|                        |                                            | C1 = 40pF                                                            | A side input from 0.9 x V <sub>DDA</sub> to<br>900mV                        | 32  | 40  | 48  |     |

| t <sub>fB</sub>        | Fall Time (SDAB, SCLB)                     | See Figure 8-1<br>R2 = 95.3Ω                                         | B side input from 0.7 x V <sub>DDB</sub> to 0.3 x V <sub>DDB</sub>          | 12  | 16  | 20  |     |

| чв                     |                                            | C2 = 400pF                                                           | B side input from 0.9 x $V_{\text{DDB}}$ to 400mV                           |     | 30  | 60  |     |

| t <sub>PLHA-B</sub>    | Propagation Delay, Side A to Side B        |                                                                      | A side input = 0.55V to B side<br>output = 0.7 x V <sub>DDB</sub>           |     | 100 | 135 |     |

| t <sub>phlab</sub>     | Propagation Delay, Side A to Side B        |                                                                      | A side input = 0.7V to B side<br>output = 0.4V                              |     | 100 | 130 |     |

| PWD <sub>AB</sub>      | Pulse Width Distortion                     | See Figure 8-1<br>R1 = 953Ω                                          | t <sub>phlab</sub> - t <sub>plhab</sub>                                     |     | 7   | 30  | ns  |

| t <sub>PLHBA</sub> 1   | Propagation Delay, Side B to Side A        | R2 = 95.3Ω<br>C1 = C2 = 10pF                                         | B side input = 0.4 x $V_{DDB}$ to A side output = 0.7 x $V_{DDA}$           |     | 80  | 100 |     |

| t <sub>phlba</sub> 1   | Propagation Delay, Side B to Side A        |                                                                      | B side input = $0.4 \times V_{DDB}$ to A side output = $0.9V$               |     | 90  | 120 |     |

| $PWD_{BA}^1$           | Pulse Width Distortion                     |                                                                      | t <sub>phlba</sub> - t <sub>plhba</sub>                                     |     | 5   | 20  |     |

| t <sub>loopa</sub> 1   | Loop propagation delay on Side A           | See Figure 8-2<br>R1 = 953Ω<br>C1 = 40pF<br>R2 = 95.3Ω<br>C2 = 400pF | A side input = 0.4V to A side<br>output = 0.3 x V <sub>DDA</sub>            |     | 200 | 220 |     |

| 4.5V ≤ (V <sub>D</sub> | <sub>DDA</sub> , V <sub>DDB</sub> ) ≤ 5.5V |                                                                      |                                                                             |     |     |     |     |

| +                      | Fall Time (SDAA, SCLA)                     | See Figure 8-1<br>R1 = 1430Ω                                         | A side input from 0.7 x V_{DDA} to 0.3 x V_{DDA}                            | 10  | 12  | 14  |     |

| t <sub>fA</sub>        |                                            | C1 = 40pF                                                            | A side input from 0.9 x $V_{\text{DDA}}$ to 900mV                           | 40  | 50  | 60  |     |

| +                      | Fall Time (SDAB, SCLB)                     | See Figure 8-1<br>R2 = 143Ω                                          | B side input from 0.7 x V_{DDB} to 0.3 x V_{DDB}                            | 8   | 10  | 12  |     |

| t <sub>fB</sub>        |                                            | C2 = 400pF                                                           | B side input from 0.9 x $V_{\text{DDB}}$ to 400mV                           | 20  | 28  | 36  |     |

| t <sub>plhab</sub>     | Propagation Delay, Side A to Side B        |                                                                      | A side input = 0.55V to B side output = $0.7 \times V_{DDB}$                |     | 100 | 120 |     |

| t <sub>phlab</sub>     | Propagation Delay, Side A to Side B        |                                                                      | A side input = 0.7V to B side<br>output = 0.4V                              |     | 70  | 90  |     |

| PWD <sub>AB</sub>      | Pulse Width Distortion                     | See Figure 8-1<br>R1 = 1430Ω                                         | t <sub>phlab</sub> - t <sub>plhab</sub>                                     |     | 30  | 45  | ns  |

| t <sub>PLHBA</sub> 1   | Propagation delay, side B to side A        | R2 = 143Ω<br>C1 = C2 = 10pF                                          | B side input = $0.4 \times V_{DDB}$ to A side output = $0.7 \times V_{DDA}$ |     | 110 | 130 |     |

| t <sub>PHLBA</sub> 1   | Propagation delay, Side B to side A        |                                                                      | B side input = $0.4 \times V_{DDB}$ to A side output = $0.9V$               |     | 100 | 150 |     |

| $PWD_{BA}^{1}$         | Pulse Width Distortion                     |                                                                      | t <sub>phlba</sub> - t <sub>plhba</sub>                                     |     | 8   | 20  |     |

| t <sub>loopa</sub> 1   | Loop propagation delay on side A           | See Figure 8-2<br>R1 = 1430Ω<br>C1 = 40pF<br>R2 = 143Ω<br>C2 = 400pF | A side input = 0.4V to A side<br>output = 0.3 x V <sub>DDA</sub>            |     | 210 | 230 |     |

8 Parameter Measurement Information

Figure 8-2 t<sub>LOOPA</sub> Test Circuit and Timing Diagram

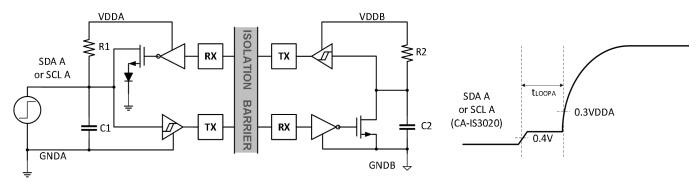

Figure 8-3 Common-Mode Transient Immunity Test Circuit

#### 9 Detailed Description

#### 9.1 Overview

The ZMCIS302x family of devices is complete dual-channel, bidirectional galvanic digital isolators with up to  $3.75kV_{RMS}$  (narrow-body package),  $5kV_{RMS}$  (wide-body package) and  $7.5kV_{RMS}$  (super wide-body package) isolation rating and  $\pm 150kV/\mu$ s typical CMTI. All devices have Schmitt trigger inputs for high noise immunity and each isolation channel has logic input and output buffer separated by capacitive silicon dioxide (SiO<sub>2</sub>) insulation barrier. The ZMCIS3020 offers two bidirectional, opendrain channels for applications, such as multi-master I<sup>2</sup>C, that require data and clock to be transmitted in both directions on the same line. The ZMCIS3021 provides an isolated I<sup>2</sup>C compatible interface supporting master mode only, with a unidirectional clock (SCL), and bidirectional data (SDA). All devices can support up to 2.0MHz operating frequency and feature independent 3.0V to 5.5V supplies (V<sub>DDA</sub> and V<sub>DDB</sub>) on each side of the isolator to setup the logic levels independently on either side, see Table 9-1 for the ZMCIS302x key features.

The ZMCIS302x family are specified over the -40°C to +125°C operating temperature range. The wide temperature range and high isolation voltage make the devices ideal for use in harsh industrial environments.

| PART NUMBER                                                                 | CHANNEL DIRECTION                          | RATED ISOLATION <sup>1</sup>                                                                                                          | MAXIMUM FREQUENCY |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| ZMCIS3020                                                                   | Bidirectional (SCL)<br>Bidirectional (SDA) | Narrow-body package: 3750V <sub>RMS</sub><br>Wide-body package: 5000V <sub>RMS</sub><br>Super wide-body package: 7500V <sub>RMS</sub> | 2MHz              |  |  |  |

| 7040102021                                                                  | Unidirectional (SCL)                       | Narrow-body package: 3750V <sub>RMS</sub>                                                                                             |                   |  |  |  |

| ZMCIS3021                                                                   | Bidirectional (SDA)                        | Wide-body package: 5000V <sub>RMS</sub>                                                                                               |                   |  |  |  |

| Note:                                                                       |                                            |                                                                                                                                       |                   |  |  |  |

| 1. For more details, please see the <i>Insulation Specifications</i> table. |                                            |                                                                                                                                       |                   |  |  |  |

#### Table 9-1 key Features

#### 9.2 Functional Block Diagrams

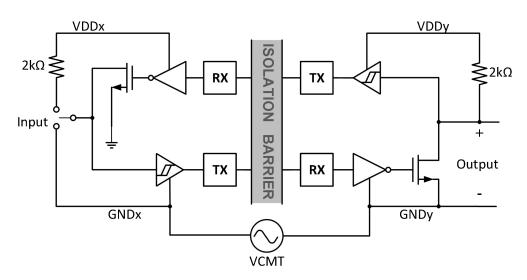

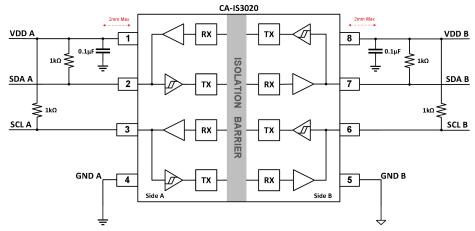

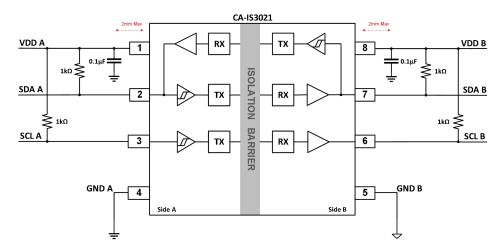

Compared with inductive isolation, the ZMCIS302x devices based on capacitive isolation can get low power at high frequency operation, reduces propagation delay and jitter, and provide good immunity to magnetic fields. See Figure 9-1 and Figure 9-2 the ZMCIS302x function block diagram for more details. To build the bidirectional signal path, the ZMCIS302x integrated two unidirectional isolated signal lines for each bidirectional line. All of output channels provide open-drain output to comply with the standard I<sup>2</sup>C interface. Side A is designed to connect to the low capacitance I<sup>2</sup>C node with up to 40pF of load capacitance, while side B is designed for connecting to a fully loaded I<sup>2</sup>C bus with up to 400pF of load capacitance.

Figure 9-1 The Block Diagram for ZMCIS3020

Figure 9-2 The Block Diagram for ZMCIS3021

#### 9.3 Device Operation Modes

Table 9-2 lists the ZMCIS302x functional modes. For optimal performance, ensure that the load capacitance on side A ( $C_A$ ) is  $\leq$  40pF, and the load capacitance on side B ( $C_B$ ) is  $\leq$  400pF. The maximum static output loading on side A is 3.5mA, while on side B, the maximum static output current is 35mA. For the bidirectional isolation channels, to prevent latch-up action, the A-side outputs comprise special buffers that regulate the logic-low voltage at approximately 700mV, and the maximum input logic-low voltage is 400mV. The internal comparator with hysteresis determines whether the logic-low level comes from the input or output based on the logic-low voltages at SDAA and SCLA pins. This prevents an output logic-low on side A from being accepted as an input low and subsequently transmitted to side B and thus preventing a latching action. The B side features conventional buffers that do not regulate logic-low output voltage. A logic-low on one side causes the corresponding pin on the other side to be pulled low while avoiding data latching within the device.

The V<sub>DDA</sub> and V<sub>DDB</sub> supplies are both internally monitored for undervoltage conditions with 1.95V minimum threshold and 2.53V maximum threshold. Undervoltage events can occur during power-up, power-down, or during normal operation due to a sagging supply voltage. When an undervoltage event is detected on either of the supplies ( $V_{DDA} \le 1.95V$  or/and  $V_{DDB} \le 1.95V$ ), all bidirectional outputs become high-impedance and are pulled high by the external pullup resistor on the open-drain outputs.

| Table 9-2 | Truth | Table |

|-----------|-------|-------|

|-----------|-------|-------|

| POWER STATE                                                              | INPUT             | OUTPUT        |  |  |  |  |

|--------------------------------------------------------------------------|-------------------|---------------|--|--|--|--|

| $V_{DDA}$ or $V_{DDB} < 1.95V$                                           | Х                 | Hi-Z          |  |  |  |  |

| $V_{DDA}$ and $V_{DDB} > 2.53V$                                          | L                 | L             |  |  |  |  |

| $V_{DDA}$ and $V_{DDB} > 2.53V$                                          | Н                 | Hi-Z          |  |  |  |  |

| $V_{DDA}$ and $V_{DDB} > 2.53V$                                          | Hi-Z <sup>2</sup> | Indeterminate |  |  |  |  |

| Notes:                                                                   |                   |               |  |  |  |  |

| 1. X = don't care; H = high level; L = low level; Hi-Z = high impedance. |                   |               |  |  |  |  |

1. X = don't care; H = high level; L = low level; Hi-Z = high impedance.

2. Invalid input condition as an I<sup>2</sup>C system requires that a pull-up resistor to VDD\_ is connected on the bus.

#### 10 Application and Implementation

#### 10.1 Overview

The Inter IC (I<sup>2</sup>C) bus is a simple, 2-wire bus for communication between different ICs (system controller, remote sensor, actuator etc. circuitry). 2-wire interfaces use only a data line (SDA) and a clock line (SCL) and allow to connect multiple slaves on the same bus without needing chip-select signals. Because 2-wire interfaces have only one data line, they can operate in half-duplex mode only, this means data can only be transmitted or received on a given cycle, also, the data line should be bidirectional. For the multi-master I<sup>2</sup>C applications, both data and clock lines need to transmit in both directions on the same line. The ZMCIS302x family of digital isolators offers two bidirectional channels (ZMCIS3020) or one unidirectional channel for clock and one bidirectional channel for data (ZMCIS3021), is ideal for use in I<sup>2</sup>C bus to provide the required isolation between different ground potentials of the system circuitry to prevent ground loop currents that otherwise may falsify the acquired

#### ZMCIS3020, ZMCIS3021 Version 1.04

data. The I<sup>2</sup>C bus can operate in Standard mode, Fast mode, or High-speed mode, with maximum data rates of 100kbps (Standard mode), 400kbps (Fast mode), 1.7Mbps (High-speed mode with  $C_{bus}$  = 400pF). The ZMCIS302x digital isolators can support up to 2.0MHz operating frequency, thus can support most of I<sup>2</sup>C communication applications.

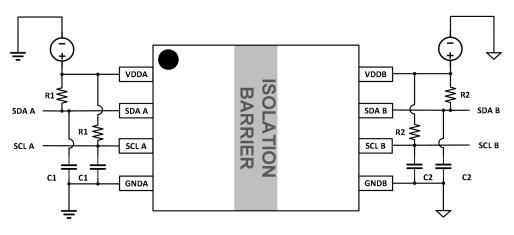

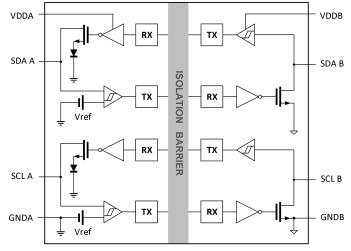

#### **10.2** Typical Application

The ZMCIS302x isolation ICs provide complete galvanic isolation between two power domains, protecting circuits from high common-mode transients and faults, eliminating ground loops. These devices do not require special power-supply sequencing, the logic levels are set independently on either side by  $V_{DDA}$  and  $V_{DDB}$ . The SDAA, SCLA, SDAB, SCLB pins have open-drain outputs, requiring pull-up resistors to their respective supplies for logic-high outputs. The output low voltages are guaranteed for sink currents of up to 35mA for side B, and 3.5mA for side A. So the minimum pullup resistors on the input lines must be selected in such a way that input current drawn is  $\leq$  3.5mA on side A and output current drawn is  $\leq$  35mA on side B. The maximum pull-up resistors on the input lines and output lines depend on the load and rise time requirements on the respective lines.

To reduce ripple and the chance of introducing data errors, bypass  $V_{DDA}$  and  $V_{DDB}$  with at least  $0.1\mu$ F low-ESR ceramic capacitors to GNDA and GNDB respectively. Place the bypass capacitors as close to the power supply input pins as possible. Figure 10-1 and Figure 10-2 show typical operating circuit of the ZMCIS3020 and ZMCIS3021.

Figure 10-1 The Typical Application Circuit for ZMCIS3020

Figure 10-2 The Typical Application Circuit for ZMCIS3021

### 11 Package Information

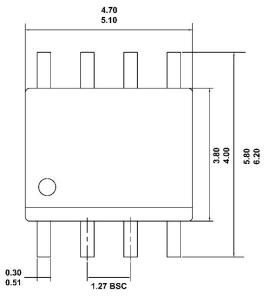

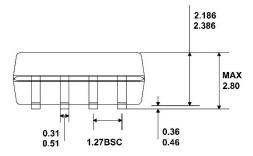

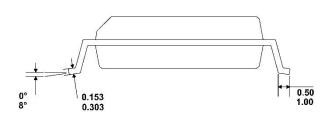

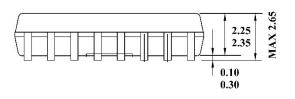

## 11.1 SOIC8 (S) Package

The values for the dimensions are shown in millimeters.

RECOMMENDED LAND PATTERN

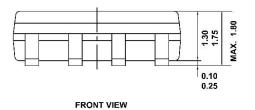

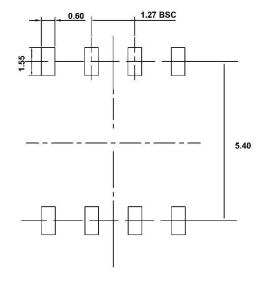

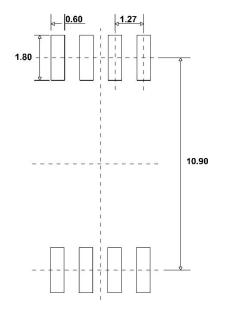

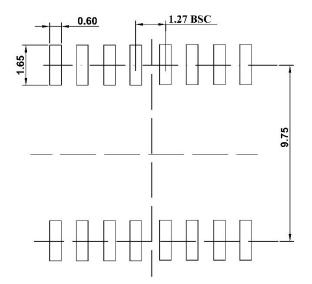

#### 11.2 SOIC8-WB (G) Package

The values for the dimensions are shown in millimeters.

**FRONT VIEW**

**Z-Micro**

## **RECOMMENDED LAND PATTERN**

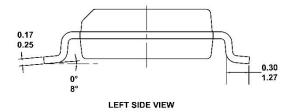

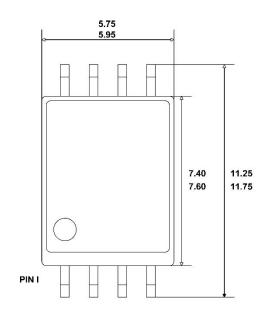

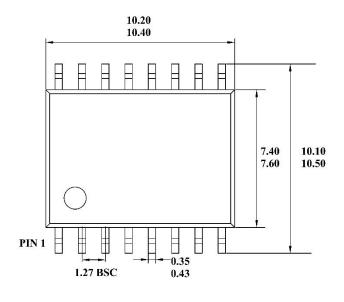

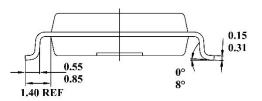

### 11.3 SOIC16-WB (W) Package

The values for the dimensions are shown in millimeters.

**TOP VIEW**

#### FRONT VIEW

#### **RECOMMENDED LAND PATTERN**

**LEFT SIDE VIEW**

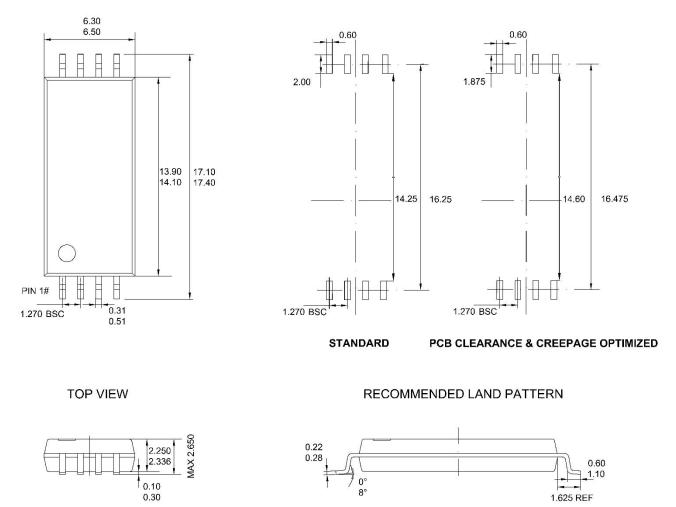

#### 11.4 SOIC8-WWB (WG) Package

The values for the dimensions are shown in millimeters.

FRONT VIEW

SIDE VIEW

**Z-Micro**

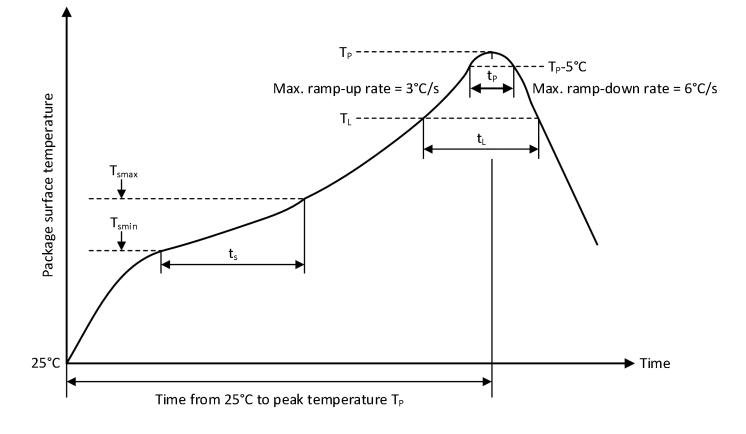

| Table 12-1 Soldering Temperature Parameters |  |

|---------------------------------------------|--|

|---------------------------------------------|--|

| Profile Feature                                                                              | Pb-Free Soldering |

|----------------------------------------------------------------------------------------------|-------------------|

| Ramp-up rate ( $T_L = 217^{\circ}C$ to peak $T_P$ )                                          | 3°C/s max         |

| Time t <sub>s</sub> of preheat temp (T <sub>smin</sub> = 150°C to T <sub>smax</sub> = 200°C) | 60~120 seconds    |

| Time t <sub>L</sub> to be maintained above 217°C                                             | 60~150 seconds    |

| Peak temperature T <sub>P</sub>                                                              | 260°C             |

| Time t <sub>P</sub> within 5°C of actual peak temp                                           | 30 seconds max    |

| Ramp-down rate (peak $T_P$ to $T_L = 217^{\circ}C$ )                                         | 6°C/s max         |

| Time from 25°C to peak temperature T <sub>P</sub>                                            | 8 minutes max     |

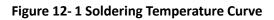

#### 13 Soldering Information

Reel Diameter

B0

К0

W QUADRANT ASSIGNMENTS FOR PIN 1 PRIENTATION CONSTANT ASSIGNMENTS FOR PIN 1 PRIENTATION CONSTANT

Dimension designed to accommodate the component length

Overall width of the carrier tape

Dimension designed to accommodate the component thickness

| $ \begin{array}{c}                                     $ | ⊖ – Sprocket Holes     |

|----------------------------------------------------------|------------------------|

| $   \phi +    \phi +    \phi$                            | User Direction of Feed |

| Pocket Quadrants                                         |                        |

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | В0<br>(mm) | КО<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ZMCIS3020S  | SOIC            | S                  | 8    | 2500 | 330                      | 12.4                     | 6.40       | 5.40       | 2.10       | 8.00       | 12.00     | Q1               |

| ZMCIS3020G  | SOIC            | G                  | 8    | 1000 | 330                      | 16.4                     | 11.95      | 6.15       | 3.20       | 16.00      | 16.00     | Q1               |

| ZMCIS3021S  | SOIC            | S                  | 8    | 2500 | 330                      | 12.4                     | 6.40       | 5.40       | 2.10       | 8.00       | 12.00     | Q1               |

| ZMCIS3021G  | SOIC            | G                  | 8    | 1000 | 330                      | 16.4                     | 11.95      | 6.15       | 3.20       | 16.00      | 16.00     | Q1               |

| ZMCIS3020W  | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.90      | 10.70      | 3.20       | 12.00      | 16.00     | Q1               |

| ZMCIS3021W  | SOIC            | W                  | 16   | 1000 | 330                      | 16.4                     | 10.90      | 10.70      | 3.20       | 12.00      | 16.00     | Q1               |

| ZMCIS3020WG | SOIC            | WG                 | 8    | 500  | 330                      | 16.4                     | 17.70      | 6.80       | 2.80       | 24.00      | 16.00     | Q1               |